Временные диаграммы преобразователя напряжение — частота

В момент, когда выходное напряжение интегратора достигает порогового значения Uп, срабатывает пороговое устройство ПУ, на входе 1 которого устанавливается логическая единица, разрешающая прохождение импульсов с выхода ГИ на ДЧ.

Как только через ДЧ пройдет количество импульсов, равное коэффициенту деления, изменяется состояние на выходе делителя ДЧ (в данном случае из состояния 1 в состояние 0). В этот момент такт TI заканчивается и начинается второй такт интегрирования — Т0, ключи К1 и К2 размыкаются.

С размыканием ключа К1 на вход интегратора через резистор R0 начинает поступать опорное напряжение U0. С размыканием ключа К2 на его выходе устанавливается логическая 1, которая подтверждает открытое состояние порогового устройства и удерживает его в этом состоянии, независимо от изменения напряжения на выходе интегратора. Таким образом, импульсы с выхода ГИ по-прежнему поступают на ДЧ.

Теперь на вход интегратора И поступают два напряжения: входное UBS. и опорное U0. Полярности их противоположны, а амплитуда опорного напряжения больше амплитуды входного. В результате воздействия разности напряжений UBX — Ur, изменение напряжения на выходе интегратора происходит в обратную сторону.

Заканчивается формирование интервала Т0 в тот момент, когда потенциал на гвыходе ДЧ снова изменится (теперь из состояния 0 в состояние 1). При этом замыкаются ключи К1 и К.2, прекращается поступление импульсов генератора на делитель. Преобразователь переходит в состояние интегрирования только входного напряжения. Затем процессы в схеме повторяются.

Заметим, что длительность такта Т0 не зависит от времязадающих элементов интегратора И, а определяется только частотой следования импульсов генератора Г И и коэффициентом деления делителя ДЧ. Так как частота генератора и коэффициент деления для данной схемы постоянны, то и длительность такта T0 также постоянна.

С увеличением входного напряжения UВX

уменьшается интервал Т1, а частота следования импульсов на выходе преобразователя увеличивается.

Таким образом, в случае идеального интегрирования зависимость выходной частоты преобразователя от входного напряжения прямо пропорциональна.

Максимальная частота на выходе преобразователя определяется по формуле fмакс = fген/n где fген — частота генератора импульса; n — коэффициент деления делителя.

Длительность интеозала T0 при скважности сигнала на выходе делителя частоты, равной 2, составляет половину периода следования импульсов с максимальной частотой T0=1/2 fмакс. В этом случае форма сигнала на выходе интегратора становится треугольной (при меньшей частоте она пилообразная).

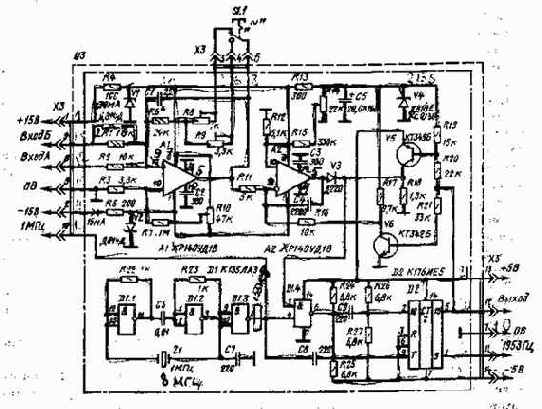

Принципиальная схема преобразователя дана на рис. 5. Усилитель УПТ и интегратор И выполнены соответственно на ОУ А1 и А2. При подаче на вход преобразователя постоянного напряжения положительной полярности сигнал поступает только на вход А.

При преобразовании постоянного напряжения отрицательной полярности или средневыпрямленного значения напряжения в цепях переменного тока используются оба входа Л и Б. В этом случае ОУ А1 работает в качестве сумматора напряжений, подаваемых по обоим входам. Так как в цепь отрицательной обратной связи включен конденсатор С1, каскад на ОУ А1 выполняет так-же функцию активного фильтра, сглаживающего пульсации выпрямленного напряжения. Переключатель S1.1 служит для корректировки результата показаний в зависимости от формы кривой переменного напряжения.