ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ КОМБИНАЦИОННОГО ТИПА

Среди ИС комбинационного типа наиболее широко используются дешифраторы, представленные в рассматриваемой серии микросхемами К165ИД1, К155ИДЗ и КЛ55ИД4.

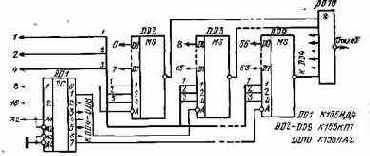

Дешифратор К155ИДЗ (рис. 16) имеет четыре адресных входа 1, 2, 4, 8, два входа стробирования А1 и А2 и шестнадцать выходов 0 — 15. Если на обоих входах стробирования уровни логического 0, на том из выходов, номер которого соответствует двоичному эквиваленту входного кода (вход 1 — младший разряд, вход 8 — старший), будет уровень логического 0, на остальных выходах — логической 1. Если хотя бы на одном из входов стробирования Al и А2 уровень логической 1, то независимо от состояний входов на всех выходах ИС формируется логическая ,1,.

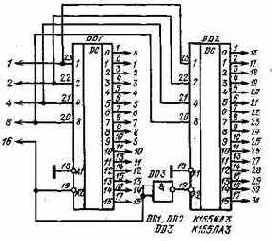

Наличие двух входов стробирования существенно расширяет возможности использования ИС. Из двух микросхем К155ИДЗ, дополненных одним ТТЛ-инвертором, можно собрать дешифратор на 32 выхода (рис. 17), дешифратор на 64 выхода собирается из четырех ИС К155ИДЗ и двух инверторов (рис. 18), а на 256 выходов — из 17 ИС К165ИДЗ (рис. 19).

Рис. 16. Выводы ИС К155ИДЗ Рис. 17. Дешифратор на 32 выхода

Интегральная микросхема К155ИД4 (рис. 20) содержит два дешифратора на четыре выхода каждый с объединенными адресными входами и раздельными входами стробирования. Уровень логического 0 на выходах первого (верхнего по схеме) дешифратора формируется (аналогично К155ИДЗ) лишь при наличии на обоих стробирующих входах уровня логического 0. Соответствующим условием для второго дешифратора является наличие на одном из его входов стробирования уровня логической 1 (вывод 1), а на другом — логического 0 (вывод 2). Такая структура ИС позволяет использовать ее в различных вариантах включения. На основе ИС К155ИД4 могут быть построены, в частности, дешифраторы на восемь выходов со входом стробирования (рис. 21) и на 16 выходов (рис. 22). На девяти ИС К155ИД4 можно собрать дешифратор на 64 выхода по схеме, подобный рис. 19.

Практически выходное напряжение ИС К155ИД1 в состоянии 0 может быть несколько выше или ниже порога переключения, поэтому для надежной работы ИС — нагрузки в минусовую цепь питания этой микросхемы следует включить кремниевый диод. Такое включение повысит порог переключения ИС примерно до 2 В, что обеспечит ее согласование с дешифратором К155ИД1. Кроме того, при этом поднимется выходной уровень логического 0 микросхемы примерно до 0,9 В, что вполне достаточно для нормальной работы последующих ИС.

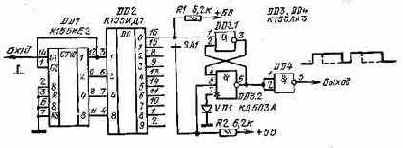

На рис. 27 приведена схема делителя частоты на 10 с переключаемой в пределах 10 — 1,1 скважностью выходных импульсов, иллюстрирующая описанные выше правила согласования дешифратора К.155ИД1 с интегральными микросхемами ТТЛ.

Для коммутации двоичных сигналов используются так называемые мульти-плексеры, представленные в серии К155 интегральными микросхемами К155КП1, К155КП2, К155КП5 и К155КТГ7.

Мультиплексер К165КП7 имеет восемь информационных входов (DO

— D7), три адресных входа (1, 2, 4) и вход стробирования А (рис. 28). У микросхемы два выхода — прямой и инверсный. Если на входе стробирования логическая 1, на прямом выходе 0 независимо от сигналов на других входах. Если на входе стробирования ИС логический 0, сигнал на прямом выходе повторяет сигнал на том входе, номер которого совпадает с двоичным эквивалентом кода на входах 1, 2, 4 мультиплексера. На инверсном выходе сигнал всегда противо-фазен сигналу на прямом выходе.

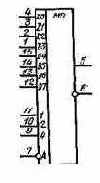

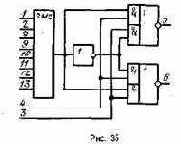

Наличие входа стробирования позволяет простыми средствами строить мультвплексеры на большее число входов. На рис. 29 приведена схема мультиплексера на 16 входов, на рис. 30 — на 64.

Мультиплексер К155КП5 (рис. 31), в отличие от К155КП7, имеет лишь инверсный выход и не имеет входа стробирования.

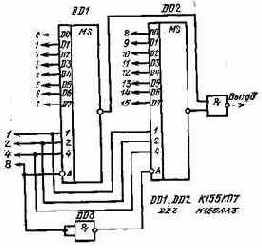

Интегральная микросхема К155КП1 (рис. 32) содержит четыре адресных входа 1, 2, 4, S, 16 информационных входов DO

— D15 и вход стробирования А. Выход у этой микросхемы только инверсный. Все свойства и способы включения у нее такие же, как и у К156КП2.

Интегральная микросхема К155КП2 (рис. 33) содержит два мультиплексе ра на четыре информационных входа D0 — D3 с отдельными входами стробирования, объединенными адресными входами и прямыми выходами.

Рис. 27. Делитель частоты на 10 с переключаемой скважностью

Рис. 28. Выводы ИС К155КП7

Рис. 29. Мультиплексер на 16 входов

Рис. 30. Мультиплексер на 64 входа Рис. 31. Выводы ИС К155КП5

Рис. 32. Выводы И С К155КП1 Рис. 33. Схема ИС К155КП2 Рис. 34. Выводы ИС К155ЛП5

Как известно, основная операция, производящаяся в цифровых вычислительных машинах, — сложение. Все другие арифметические операции — вычитание, умножение, деление — сводятся к сложению. Операция сложения двоичных чисел производится с использованием сумматоров и полусумматоров.

В состав серии ИС К155 входят два типа полусумматоров — К155ЛП5 и К155ИП2.

В ИС К155ЛП5 (рис. 34) четыре независимых полусумматора (другие названия — сумматор по модулю два, элемент Исключительное ИЛИ). Каждый из этих элементов работает следующим образом. Если на обоих входах элемента, например 1 и 2, уровень логического 0 — на выходе 3 логический 0. Если на одном из входов логический 0, на другом логическая 1, на выходе — 1,. если на обоих входах — 1, на выходе 0.

Рис. 35. Схема ИС К155ИП2

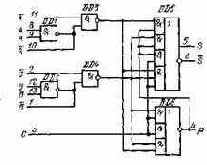

В состав ИС КД55ИП2 (рис. 35) входят восьмивходовый сумматор по мо-Дулю 2, обозначенный SM2, инвертор и два логических элемента И — ИЛИ — НЕ;.

Восьмивходовый сумматор по модулю 2 работает аналогично двухвходовому: если на его входах четное число сигналов с уровнем логической 1, на выходе логический 0, если число единиц на входах нечетное, на выходе 1. Остальные элементы ИС позволяют объединять интегральные микросхемы между собой для увеличения числа входов. При подаче уровня логической 1 на вход 3, логического 0 на вход 4, уровень на выходе 5 будет соответствовать выходному уровню сумматора SM2, на выходе 6 — его инверсии.

Бели уровни на (входах 3 и 4 изменить на противоположные, уровни на выходах 5 и 6 также изменятся на противоположные.

Напомним основные свойства двоичных сумматоров. Каждый разряд двоичного сумматора (его иногда называют полным сумматором) имеет три входа — два входа Л и В для слагаемых, вход сигнала переноса от предыдущего разряда С и два выхода — суммы S и сигнала переноса Р в следующий разряд. Работа сумматора иллюстрируется табл. 3. Входы А, В, С, вообще говоря, равноправны. Сигнал суммы S принимает значение логической ,1 при нечетном числе единиц на входах А, В и С и логического 0 при четном, как и в рассмотренных выше полусумматорах. Сигнал переноса Р равен логической 1 при числе единиц на входах, равном 2 или 3. Интересным свойством табл. 3 является ее симметрия: замена 0 на 1 и наоборот не нарушает ее истинности. Это свойство используется для упрощения схем сумматоров.

Таблица 3

|

Входы |

Выходы |

Входы |

Выходы |

||||||

|

Л |

в |

с |

S |

р |

А |

в |

с |

S |

р |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Если на всех входах сигналы отсутствуют (А = В = С = 0), выходные сигналы также отсутствуют: S = 0, Р=0 (Р=0).

Входные сигналы А и В могут быть поданы не только в прямом коде (входы 8 и 9 для А, 12 и 13 для В), но и в инверсном (входы 11 для А и 2 для В). При использовании инверсных входных сигналов входы 8, 9, 12 и 13 следует соединить с общим проводом, а при использовании прямых сигналов — попарно соединить выводы 10 и 11, 1 и 2.

Элементы DD1 и DD2 микросхемы имеют открытый коллекторный выход, поэтому выводы 10 и 1 могут использоваться или как выходы элементов DD1 и DD2, или как входы, превращающие элементы DD1 и DD2 типа И — НЕ в элементы И — ИЛИ — НЕ подключением к этим выводам выходов ИС К155ЛА8. В любом случае использования выводов 10 и 1 между ними и плюсом питания необходимо включать резисторы 1 — 2 кОм.

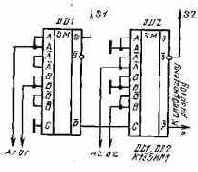

Рис. 36. Схема ИС К155ИМ1

Рис. 37. Схема соединения интегральных микросхем К155ИМ1 в двухразрядный сумматор

Рис. 38. Выводы ИС К155ИМ2 Рис. 39. Выводы ИС К155ИМЗ

При соединении ИС К155ИМ1 в многоразрядный сумматор (рис. 37) используется описанное выше свойство симметрии полного сумматора относительно замены входных и выходных сигналов инверсными. В первом разряде входные сигналы подаются на прямые входы ИС DD1, выходной сигнал суммы снимается с прямого выхода S, сигнал переноса — с единственного (инверсного) выхода Р. На второй разряд сумматора входные сигналы А и В подаются на инверсные входы, на прямой вход С подается инверсный сигнал переноса с первого разряда, выходной прямой сигнал суммы формируется на инверсном выходе 5, выходной прямой сигнал переноса — на инверсном выходе Р. Третий разряд сумматора работает так же, как и первый, четвертый — как второй и т. д.

Такое чередование режима работы одноразрядных сумматоров обеспечивает минимальную задержку распространения сигнала в самой длинной цепи — в цепи формирования сигнала переноса.

Интегральная микросхема К155ИМ2 (ряс. 38) представляет собой объединение двух микросхем К155ИМ1, соединенных в соответствии с рис. 37 с исключенными неиспользуемыми инверторами. Интегральная микросхема К155ИМЗ (рис. 39) соответствует двум микросхемам К155ИМ2, в которых вы-:ход переноса первой ИС соединен со входом С второй.

ЭЛЕКТРОННЫЕ ЧАСЫ